# **LAMPIRAN**

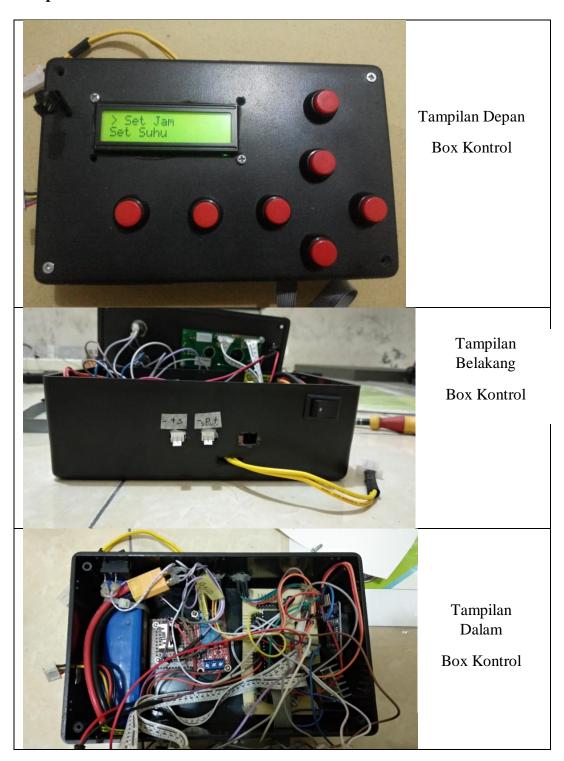

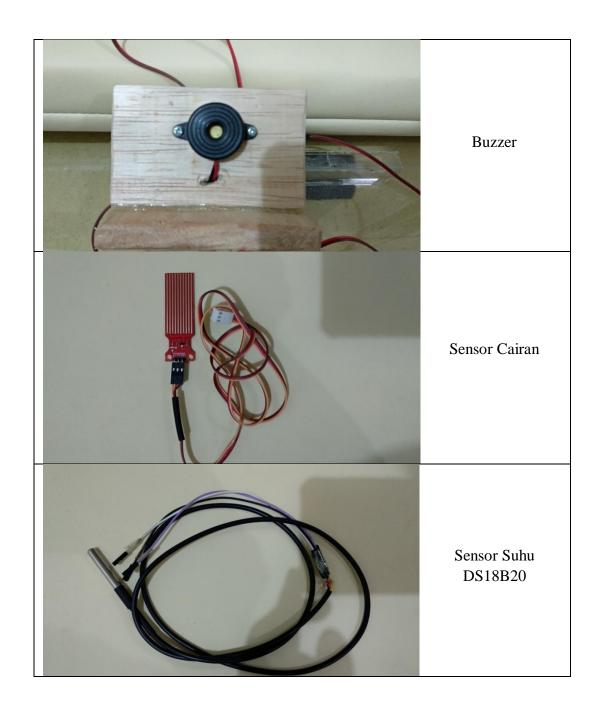

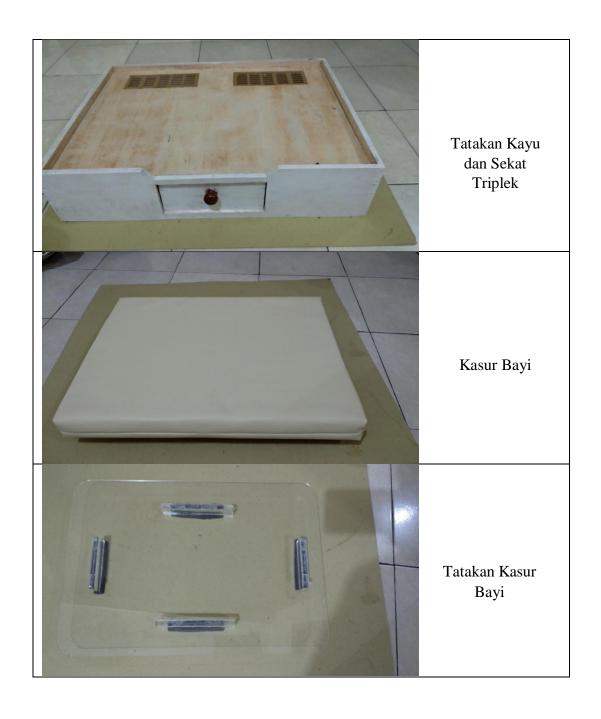

# Lampiran 1. Foto Alat

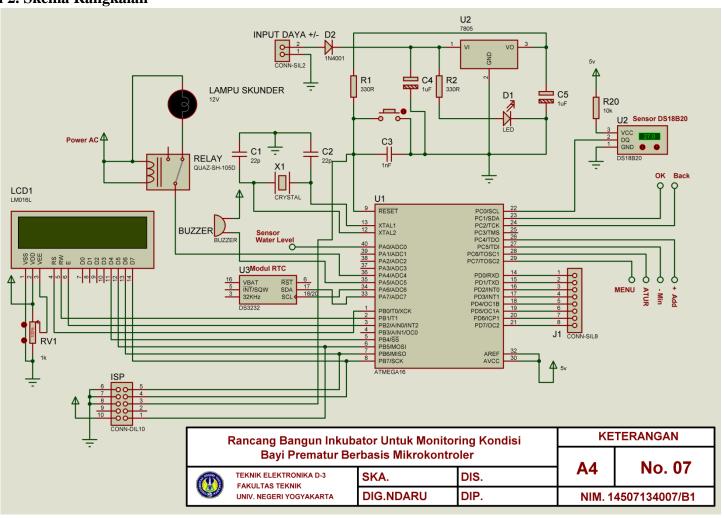

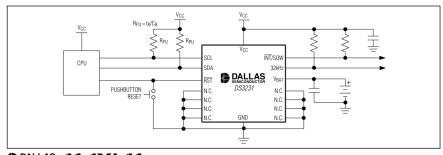

Lampiran 2. Skema Rangkaian

# Lampiran 3. Progam Alat

```

/*************

This program was produced by the

CodeWizardAVR V2.05.0 Advanced

Automatic Program Generator

© Copyright 1998-2010 Pavel Haiduc, HP InfoTech s.r.l.

http://www.hpinfotech.com

Project:

Version :

Date : 30/04/2016

Author : www.Eca.ir *** www.Webkade.ir

Company :

Comments:

Chip type

: ATmega16

Program type : Application

AVR Core Clock frequency: 16,000000 MHz

Memory model : Small

: 0

External RAM size

Data Stack size : 256

***********************************

#include <mega16.h>

#include <delay.h>

#include <1wire.h>

#include <ds18b20.h>

#include <alcd.h>

#include <i2c.h>

#include <stdlib.h>

#include <string.h>

#include <ds1307.h>

#define MAX DS1820 8

unsigned char ds18b20 devices;

unsigned char ds18b20 rom codes[MAX DS1820][9];

#include <stdio.h>

#define ADC VREF TYPE 0x20

#define s2 PINC.1 //select

#define s4 PINC.2 //back

#define s6 PINC.4 //-

#define s5 PINC.5 //+

#define s3 PINC.6 //atur

#define s1 PINC.7 //menu

unsigned char read adc(unsigned char adc input)

ADMUX=adc input | (ADC VREF TYPE & 0xff);

```

```

// Delay needed for the stabilization of the ADC input

voltage

delay_us(10);

// Start the AD conversion

ADCSRA = 0 \times 40;

// Wait for the AD conversion to complete

while ((ADCSRA \& 0x10) == 0);

ADCSRA = 0 \times 10;

return ADCH;

float temp;

unsigned char i; // variabel yang digunakan

float dadc, dadc1;

unsigned char jam, menit, detik;

char buff[33],buffer[33];

eeprom unsigned char ea=0,em=0;

int x, nol, satu, dua, sjam, smenit, sdetik, var, var1, var2;

int baca(char x)

dadc1 = read adc(x);

dadc = (float) dadc1*5/255; // baca adc

return dadc;

void baca rtc()

rtc get time(&jam, &menit, &detik); // baca adc

void ceksensor()

lcd clear();

while(1){

if(!s3){x++;delay_ms(200);} // baca sensor cairan

if (x>0) x=0;

if(x==0){

nol=read adc(0);

lcd qotoxy(0,0);

sprintf(buff,"0: %d ",nol);

lcd puts(buff);

delay ms(100);

satu=read adc(1);

lcd_gotoxy(0,1);

sprintf(buffer,"1: %d ",satu);

lcd_puts(buffer);

delay ms(100);

```

```

dua=read adc(2); delay ms(100);

lcd gotoxy(10,0);

sprintf(buff,"2: %d ",dua);

lcd puts(buff);

if(!s4) \{delay_ms(300);

lcd clear();

break;

}

}

}

void set_suhu(){

lcd clear();

while(1){

if (!s3) \{x++; delay_ms(300); \}

if(x>60) x=0;

// seting nilai suhu

if (x<0) x=60; {

lcd gotoxy(0,0);

sprintf(buff, "Set Suhu : %d", var);

lcd_puts(buff);

if(!s5) {var++; delay_ms(200);}

if(!s6) {var--; delay ms(200);}

if(var<0)var=0;</pre>

if (var>60) var=0;

if(!s4) \{delay_ms(300);

lcd clear();

break;

}

}

}

void set jam()

sjam=jam;

smenit=menit;

sdetik=detik;

while(1) {

rtc_set_time(sjam, smenit, sdetik);

if(!s3){x++;delay_ms(300);} // seting waktu

if (x>2) x=0;

if(x==0){

lcd gotoxy(0,0);

");

lcd putsf("Set Jam

```

```

lcd gotoxy(0,1);

sprintf(buff," [%02d]:%02d:%02d ",sjam,smenit,sdetik);

lcd puts(buff);

if(!s5){sjam++;delay_ms(200);}

if(!s6){sjam--;delay ms(200);}

if(sjam>23)sjam=0;

if (sjam<0) sjam=23;

if(x==1){

lcd_gotoxy(0,0);

lcd putsf("Set Menit

lcd_gotoxy(0,1);

sprintf(buff," %02d:[%02d]:%02d ",sjam,smenit,sdetik);

lcd puts(buff);

if(!s5){smenit++;delay_ms(200);}

if(!s6) {smenit--; delay ms(200);}

if (smenit>59) smenit=0;

if (smenit<0) smenit=59;</pre>

if(x==2){

lcd gotoxy(0,0);

lcd putsf("Set Detik

");

lcd gotoxy(0,1);

sprintf(buff," %02d:%02d:[%02d] ",sjam,smenit,sdetik);

lcd puts(buff);

if(!s5) {sdetik++;delay ms(200);}

if(!s6) {sdetik--; delay ms(200);}

if(sdetik>59)sdetik=0;

if(sdetik<0)sdetik=59;

if(!s4) {delay_ms(300);break;}

}

void set alarm() {

lcd clear();

while(1){

if(!s3) \{x++; delay_ms(300);\} // seting alarm

if (x>1) x=0;

if(x==0) {

lcd gotoxy(0,0);

sprintf(buff,"[%d]:%d ",var1,var2);

lcd puts(buff);

// seting input waktu alarm

if(!s5) {var1++; delay ms(200);}

if(!s6) {var1--;delay_ms(200);}

if (var1>24) var1=0;

if (var1<0) var1=0;

}

```

```

if(x==1){

lcd gotoxy(0,0);

sprintf(buff,"%d:[%d] ",var1,var2);

lcd puts(buff);

if(!s5){var2++;delay ms(200);// seting input waktu alarm

if(!s6) {var2--;delay_ms(200);}

if (var2>59) var2=0;

if (var2<0) var2=59;

if(!s4) \{delay ms(300);

lcd clear();

break;

}

}

/**************

*******

void setting()

while(1){

if (!s3) \{x++; delay ms(300); \}

if (x>3) x=0;

if(x==0) {

lcd gotoxy(0,0);

lcd putsf("> Set Jam ");

lcd gotoxy(0,1);

");

lcd putsf("Set Suhu

if(!s2){delay ms(300);set jam();}

}

if(x==1){

lcd gotoxy(0,0);

lcd_putsf("Set Jam

");

// tampilan menu pada LCD

lcd gotoxy(0,1);

lcd_putsf("> Set Suhu

");

if(!s2){delay ms(300);set suhu();}

if(x==2){

lcd gotoxy(0,0);

lcd putsf("> Set Alarm ");

lcd gotoxy(0,1);

lcd putsf("Cek Sensor");

if(!s2) {delay ms(300); set alarm();}

if(x==3) {

lcd gotoxy(0,0);

lcd putsf("Set Alarm

");

lcd gotoxy(0,1);

```

```

lcd putsf("> Cek Sensor

if(!s2) {delay_ms(300);ceksensor();}

if(!s4){

delay ms(300);

lcd clear();

break;

/***************

********

void main(void)

PORTA=0 \times 00;

DDRA=0 \times 00;

PORTB=0x00;

DDRB=0xff;

PORTC=0xff;

DDRC=0 \times 00;

PORTD=0xF8;

DDRD=0 \times 00;

TCCR0=0x00;

TCNT0=0x00;

OCR0=0x00;

TCCR1A=0xA1;

TCCR1B=0x03;

TCNT1H=0x00;

TCNT1L=0x00;

ICR1H=0x00;

ICR1L=0 \times 00;

OCR1AH=0x00;

OCR1AL=0x00;

OCR1BH=0x00;

OCR1BL=0x00;

ASSR=0 \times 00;

TCCR2=0x00;

TCNT2=0x00;

OCR2=0x00;

MCUCR=0x00;

MCUCSR=0x00;

// Timer(s)/Counter(s) Interrupt(s) initialization

TIMSK=0x00;

UCSRA=0 \times 00;

UCSRB=0x18;

UCSRC=0x86;

```

```

UBRRH=0x00;

UBRRL=0x67;

ACSR=0x80;

SFIOR=0x00;

ADMUX=ADC VREF TYPE & 0xff;

ADCSRA=0xA4;

SFIOR&=0x1F;

SPCR=0x00;

TWCR=0 \times 00;

lcd init(16);

//rtc set time(14,8,00);

lcd gotoxy(0,0);

lcd putsf("Wait..");

delay ms(100);

w1 init();

ds18b20 devices=w1 search(0xf0,ds18b20 rom codes);

lcd clear();

goto next;

exit:

setting();

next:

// output buzzer

// output buzzer

//

PORTA.5=1;

DDRA.5=1;

//output relay

// output relay

DDRA.4=1;

PORTA.4=1;

while (1)

if(!s1) {delay_ms(300);goto exit;}

baca rtc();

delay_ms(100);

// baca nilai suhu

nol=read adc(0);

delay ms(100);

dua=read adc(2);

delay_ms(50);

if(detik%3==0){

for(i=0;i<ds18b20 devices;i++)</pre>

temp=ds18b20 temperature(ds18b20 rom codes[i]);

if(temp<var)PORTA.4=0; //relay off >> lampu on

if(temp>var)PORTA.4=1; //relay on >> lampu mati

```

```

for (i=0;i<8;i++)

baca(i);

}

}

if (PINC.2==0) {ea=jam; ea=ea+var; em=menit;

em=em+var2;

lcd gotoxy(0,1);

lcd putsf("Saved");delay ms(200); lcd clear();}

if(jam==ea && menit==em) PORTA.5=0; //buzzer on

// seting alarm

if (PINC.6==0) {ea=0; em=0; PORTA.5=1;

lcd gotoxy(0,1);

lcd putsf("Clear");delay ms(200); lcd clear();}

lcd gotoxy(0,0);

sprintf(buff, "%02d:%02d:%02d ", jam, menit, detik);

lcd puts(buff);

lcd gotoxy(10,0);

sprintf(buff,"%0.1fc ",temp);

lcd puts(buff);

//lampu mati

if(temp>var)PORTA.4=1;

lcd gotoxy(10,1);

lcd putsf("[MENU]");

if(nol>51){nol=read\_adc(0); // progam baca sensor}

cairan on

lcd gotoxy(0,1);

lcd putsf("NGOMPOL");

PORTA.5=0; // buzzer on

}

sensor cairan off

lcd gotoxy(0,1);

");

lcd putsf("

PORTA.5=1; //off

if(PINC.6==0){PORTA.5=1;} //off manual buzzer

}

}

```

# Lampiran 4. Datasheet ATMega16

#### **Features**

- High-performance, Low-power AVR® 8-bit Microcontroller

Advanced RISC Architecture

- - 131 Powerful Instructions Most Single-clock Cycle Execution

- 32 x 8 General Purpose Working Registers

- Fully Static OperationUp to 16 MIPS Throughput at 16 MHz

- On-chip 2-cycle Multiplier

Nonvolatile Program and Data Memories

- 16K Bytes of In-System Self-Programmable Flash Endurance: 10,000 Write/Erase Cycles

- Optional Boot Code Section with Independent Lock Bits In-System Programming by On-chip Boot Program

True Read-While-Write Operation

– 512 Bytes EEPROM

- Endurance: 100,000 Write/Erase Cycles

- 1K Byte Internal SRAM

- Programming Lock for Software Security

- JTAG (IEEE std. 1149.1 Compliant) Interface

Boundary-scan Capabilities According to the JTAG Standard

- Extensive On-chip Debug Support

Programming of Flash, EEPROM, Fuses, and Lock Bits through the JTAG Interface

- Peripheral Features

Two 8-bit Timer/Counters with Separate Prescalers and Compare Modes

One 16-bit Timer/Counter with Separate Prescaler, Compare Mode, and Capture Mode

- Real Time Counter with Separate Oscillator

Four PWM Channels

8-channel, 10-bit ADC

- 8 Single-ended Channels 7 Differential Channels in TQFP Package Only

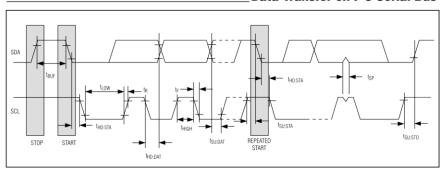

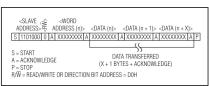

- 2 Differential Channels with Programmable Gain at 1x, 10x, or 200x Byte-oriented Two-wire Serial Interface

- Programmable Serial USART

Master/Slave SPI Serial Interface

- Programmable Watchdog Timer with Separate On-chip Oscillator

- On-chip Analog Comparator Special Microcontroller Features

- - Power-on Reset and Programmable Brown-out Detection

Internal Calibrated RC Oscillator

- External and Internal Interrupt Sources

Six Sleep Modes: Idle, ADC Noise Reduction, Power-save, Power-down, Standby and Extended Standby

- I/O and Packages

- 32 Programmable I/O Lines

40-pin PDIP, 44-lead TQFP, and 44-pad MLF

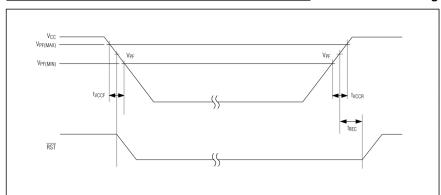

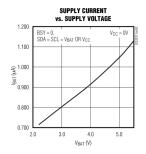

- Operating Voltages

- 2.7 5.5V for ATmega16L

4.5 5.5V for ATmega16

- Speed Grades

0 8 MHz for ATmega16L

- 0 16 MHz for ATmega16

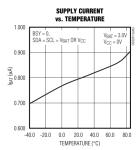

Power Consumption @ 1 MHz, 3V, and 25°C for ATmega16L

- Active: 1.1 mA

- Idle Mode: 0.35 mA

- Power-down Mode: < 1 μA

8-bit AVR Microcontroller with 16K Bytes In-System **Programmable** Flash

ATmega16 ATmega16L

Summary

Note: This is a summary document. A complete document is available on our Web site at www.atmel.com

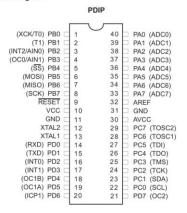

# **Pin Configurations**

Figure 1. Pinouts ATmega16

# Disclaimer

Typical values contained in this datasheet are based on simulations and characterization of other AVR microcontrollers manufactured on the same process technology. Min and Max values will be available after the device is characterized.

# 2 ATmega16(L) =

## Overview

The ATmega16 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the ATmega16 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

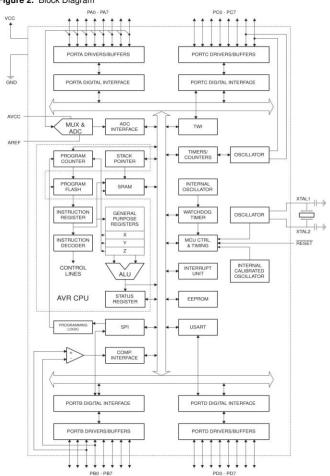

## **Block Diagram**

Figure 2. Block Diagram

— <u>Aimei</u>

3

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The ATmega16 provides the following features: 16K bytes of In-System Programmable Flash Program memory with Read-While-Write capabilities, 512 bytes EEPROM, 1K byte SRAM, 32 general purpose I/O lines, 32 general purpose working registers, a JTAG interface for Boundary-scan, On-chip Debugging support and programming, three flexible Timer/Counters with compare modes, Internal and External Interrupts, a serial programmable USART, a byte oriented Two-wire Serial Interface, an 8-channel, 10-bit ADC with optional differential input stage with programmable gain (TQFP package only), a programmable Watchdog Timer with Internal Oscillator, an SPI serial port, and six software selectable power saving modes. The Idle mode stops the CPU while allowing the USART, Two-wire interface, A/D Converter, SRAM, Timer/Counters, SPI port, and interrupt system to continue functioning. The Power-down mode saves the register contents but freezes the Oscillator, disabling all other chip functions until the next External Interrupt or Hardware Reset. In Power-save mode, the Asynchronous Timer continue to run, allowing the user to maintain a timer base while the rest of the device is sleeping. The ADC Noise Reduction mode stops the CPU and all I/O modules except Asynchronous Timer and ADC, to minimize switching noise during ADC conversions. In Standby mode, the crystal/resonator Oscillator is running while the rest of the device is sleeping. This allows very fast start-up combined with low-power consumption. In Extended Standby mode, both the main Oscillator and the Asynchronous Timer continue to run.

The device is manufactured using Atmel's high density nonvolatile memory technology. The On-chip ISP Flash allows the program memory to be reprogrammed in-system through an SPI serial interface, by a conventional nonvolatile memory programmer, or by an On-chip Boot program running on the AVR core. The boot program can use any interface to download the application program in the Application Flash memory. Software in the Boot Flash section will continue to run while the Application Flash section is updated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATmega16 is a powerful microcontroller that provides a highly-flexible and cost-effective solution to many embedded control applications.

The ATmega16 AVR is supported with a full suite of program and system development tools including: C compilers, macro assemblers, program debugger/simulators, in-circuit emulators, and evaluation kits.

#### **Pin Descriptions**

VCC Digital supply voltage.

GND Ground

Port A (PA7..PA0) Port A serves as the analog inputs to the A/D Converter.

Port A also serves as an 8-bit bi-directional I/O port, if the A/D Converter is not used. Port pins can provide internal pull-up resistors (selected for each bit). The Port A output buffers have symmetrical drive characteristics with both high sink and source capability. When pins PA0 to PA7 are used as inputs and are externally pulled low, they will source current if the internal pull-up resistors are activated. The Port A pins are tri-stated when a reset condition becomes active, even if the clock is not running.

# 4 ATmega16(L) =

# ATmega16(L)

Port B (PB7..PB0)

Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port B also serves the functions of various special features of the ATmega16 as listed

Port C (PC7..PC0) Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each

bit). The Port C output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active, even if the clock is not running. If the JTAG interface is enabled, the pull-up resistors on pins PC5(TDI), PC3(TMS) and PC2(TCK) will be acti-

vated even if a reset occurs.

Port C also serves the functions of the JTAG interface and other special features of the ATmega16 as listed on page 59.

Port D (PD7..PD0) Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each

bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset

condition becomes active, even if the clock is not running.

Port D also serves the functions of various special features of the ATmega16 as listed

on page 61.

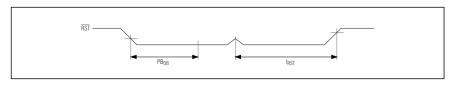

RESET

Reset Input. A low level on this pin for longer than the minimum pulse length will generate a reset, even if the clock is not running. The minimum pulse length is given in Table

15 on page 36. Shorter pulses are not guaranteed to generate a reset.

XTAL1 Input to the inverting Oscillator amplifier and input to the internal clock operating circuit.

XTAL2 Output from the inverting Oscillator amplifier.

AVCC is the supply voltage pin for Port A and the A/D Converter. It should be externally connected to  $V_{CC}$ , even if the ADC is not used. If the ADC is used, it should be connected to  $V_{CC}$  through a low-pass filter. AVCC

AREF AREF is the analog reference pin for the A/D Converter.

5

# **Register Summary**

| Address              | Name   | Bit 7           | Bit 6             | Bit 5              | Bit 4    | Bit 3  | Bit 2  | Bit 1    | Bit 0  | Page              |

|----------------------|--------|-----------------|-------------------|--------------------|----------|--------|--------|----------|--------|-------------------|

| \$3F (\$5F)          | SREG   | 1               | т                 | н                  | s        | V      | N      | Z        | С      | 7                 |

| \$3E (\$5E)          | SPH    | _               | -                 | -                  | -        | -      | SP10   | SP9      | SP8    | 10                |

| \$3D (\$5D)          | SPL    | SP7             | SP6               | SP5                | SP4      | SP3    | SP2    | SP1      | SP0    | 10                |

| \$3C (\$5C)          | OCR0   |                 | r0 Output Compa   |                    |          |        | 0.2    |          |        | 83                |

| \$3B (\$5B)          | GICR   | INT1            | INTO              | INT2               | _        | _      | _      | IVSEL    | IVCE   | 46, 67            |

| \$3A (\$5A)          | GIFR   | INTF1           | INTF0             | INTF2              | -        |        |        | IVOEL    | IVOL   | 68                |

|                      |        |                 |                   |                    | 001544   | 001540 | TOIE1  | OCIFO    | TOIE0  |                   |

| \$39 (\$59)          | TIMSK  | OCIE2           | TOIE2             | TICIE1             | OCIE1A   | OCIE1B |        | OCIE0    |        | 83, 114, 132      |

| \$38 (\$58)          | TIFR   | OCF2            | TOV2              | ICF1               | OCF1A    | OCF1B  | TOV1   | OCF0     | TOV0   | 84, 115, 132      |

| \$37 (\$57)          | SPMCR  | SPMIE           | RWWSB             | -                  | RWWSRE   | BLBSET | PGWRT  | PGERS    | SPMEN  | 249               |

| \$36 (\$56)          | TWCR   | TWINT           | TWEA              | TWSTA              | TWSTO    | TWWC   | TWEN   | -        | TWIE   | 178               |

| \$35 (\$55)          | MCUCR  | SM2             | SE                | SM1                | SM0      | ISC11  | ISC10  | ISC01    | ISC00  | 30, 66            |

| \$34 (\$54)          | MCUCSR | JTD             | ISC2              | _                  | JTRF     | WDRF   | BORF   | EXTRF    | PORF   | 39, 67, 229       |

| \$33 (\$53)          | TCCR0  | FOC0            | WGM00             | COM01              | COM00    | WGM01  | CS02   | CS01     | CS00   | 81                |

| \$32 (\$52)          | TCNT0  | Timer/Counter   | r0 (8 Bits)       |                    |          |        |        |          |        | 83                |

|                      | OSCCAL | Oscillator Cali | bration Register  |                    |          |        |        |          |        | 28                |

| \$31(1) (\$51)(1)    | OCDR   | On-Chip Debu    |                   |                    |          |        |        |          |        | 225               |

| \$30 (\$50)          | SFIOR  | ADTS2           | ADTS1             | ADTS0              | _        | ACME   | PUD    | PSR2     | PSR10  | 55,86,133,199,219 |

| \$2F (\$4F)          | TCCR1A | COM1A1          | COM1A0            | COM1B1             | COM1B0   | FOC1A  | FOC1B  | WGM11    | WGM10  | 109               |

| \$2E (\$4E)          | TCCR1B | ICNC1           | ICES1             | COMIDI             | WGM13    | WGM12  | CS12   | CS11     | CS10   | 112               |

|                      |        |                 |                   | -                  | WGWI3    | WGM12  | US12   | CSII     | CSTO   |                   |

| \$2D (\$4D)          | TCNT1H |                 | r1 - Counter Reg  |                    |          |        |        |          |        | 113               |

| \$2C (\$4C)          | TCNT1L |                 | r1 - Counter Reg  |                    |          |        |        |          |        | 113               |

| \$2B (\$4B)          | OCR1AH |                 |                   | are Register A Hi  |          |        |        |          |        | 113               |

| \$2A (\$4A)          | OCR1AL |                 |                   | oare Register A Lo |          |        |        |          |        | 113               |

| \$29 (\$49)          | OCR1BH | Timer/Counter   | r1 – Output Comp  | are Register B Hi  | igh Byte |        |        |          |        | 113               |

| \$28 (\$48)          | OCR1BL | Timer/Counter   | r1 - Output Comp  | oare Register B Lo | ow Byte  |        |        |          |        | 113               |

| \$27 (\$47)          | ICR1H  | Timer/Counter   | r1 - Input Captur | Register High B    | yte      |        |        |          |        | 114               |

| \$26 (\$46)          | ICR1L  | Timer/Counter   | r1 - Input Captur | Register Low By    | /te      |        |        | 0.0      |        | 114               |

| \$25 (\$45)          | TCCR2  | FOC2            | WGM20             | COM21              | COM20    | WGM21  | CS22   | CS21     | CS20   | 127               |

| \$24 (\$44)          | TCNT2  | Timer/Counter   |                   |                    |          |        |        |          |        | 129               |

| \$23 (\$43)          | OCR2   |                 | r2 Output Compa   | re Register        |          |        |        |          |        | 129               |

| \$22 (\$42)          | ASSR   | Tilliel/Courte  | Te Output Compa   | Terregiator        |          | AS2    | TCN2UB | OCR2UB   | TCR2UB | 130               |

|                      |        | -               | _                 | _                  |          |        | WDP2   | WDP1     |        |                   |

| \$21 (\$41)          | WDTCR  | -               | -                 | -                  | WDTOE    | WDE    |        |          | WDP0   | 41                |

| \$20(2) (\$40)(2)    | UBRRH  | URSEL           |                   | -                  | -        |        |        | RR[11:8] |        | 165               |

| 10 (100) - 70 (7.57) | UCSRC  | URSEL           | UMSEL             | UPM1               | UPM0     | USBS   | UCSZ1  | UCSZ0    | UCPOL  | 164               |

| \$1F (\$3F)          | EEARH  | -               | -                 |                    | -        | (E)    | -      | -        | EEAR8  | 17                |

| \$1E (\$3E)          | EEARL  |                 | fress Register Lo | w Byte             |          |        |        |          |        | 17                |

| \$1D (\$3D)          | EEDR   | EEPROM Dat      | a Register        |                    |          |        |        |          |        | 17                |

| \$1C (\$3C)          | EECR   | -               | -                 | -                  | -        | EERIE  | EEMWE  | EEWE     | EERE   | 17                |

| \$1B (\$3B)          | PORTA  | PORTA7          | PORTA6            | PORTA5             | PORTA4   | PORTA3 | PORTA2 | PORTA1   | PORTA0 | 64                |

| \$1A (\$3A)          | DDRA   | DDA7            | DDA6              | DDA5               | DDA4     | DDA3   | DDA2   | DDA1     | DDA0   | 64                |

| \$19 (\$39)          | PINA   | PINA7           | PINA6             | PINA5              | PINA4    | PINA3  | PINA2  | PINA1    | PINA0  | 64                |

| \$18 (\$38)          | PORTB  | PORTB7          | PORTB6            | PORTB5             | PORTB4   | PORTB3 | PORTB2 | PORTB1   | PORTB0 | 64                |

| \$17 (\$37)          | DDRB   | DDB7            | DDB6              | DDB5               | DDB4     | DDB3   | DDB2   | DDB1     | DDB0   | 64                |

| \$17 (\$37)          | PINB   | PINB7           | PINB6             | PINB5              | PINB4    | PINB3  | PINB2  | PINB1    | PINB0  | 64                |

|                      |        |                 |                   |                    |          |        |        |          |        |                   |

| \$15 (\$35)          | PORTC  | PORTC7          | PORTC6            | PORTC5             | PORTC4   | PORTC3 | PORTC2 | PORTC1   | PORTC0 | 65                |

| \$14 (\$34)          | DDRC   | DDC7            | DDC6              | DDC5               | DDC4     | DDC3   | DDC2   | DDC1     | DDC0   | 65                |

| \$13 (\$33)          | PINC   | PINC7           | PINC6             | PINC5              | PINC4    | PINC3  | PINC2  | PINC1    | PINC0  | 65                |

| \$12 (\$32)          | PORTD  | PORTD7          | PORTD6            | PORTD5             | PORTD4   | PORTD3 | PORTD2 | PORTD1   | PORTD0 | 65                |

| \$11 (\$31)          | DDRD   | DDD7            | DDD6              | DDD5               | DDD4     | DDD3   | DDD2   | DDD1     | DDD0   | 65                |

| \$10 (\$30)          | PIND   | PIND7           | PIND6             | PIND5              | PIND4    | PIND3  | PIND2  | PIND1    | PIND0  | 65                |

| \$0F (\$2F)          | SPDR   | SPI Data Reg    | jister            |                    |          |        |        |          |        | 140               |

| \$0E (\$2E)          | SPSR   | SPIF            | WCOL              | -                  | -        | -      | -      | -        | SPI2X  | 140               |

| \$0D (\$2D)          | SPCR   | SPIE            | SPE               | DORD               | MSTR     | CPOL   | CPHA   | SPR1     | SPR0   | 138               |

| \$0C (\$2C)          | UDR    | USART I/O D     |                   |                    |          |        |        |          |        | 161               |

| \$0B (\$2B)          | UCSRA  | RXC             | TXC               | UDRE               | FE       | DOR    | PE     | U2X      | MPCM   | 162               |

|                      |        | RXCIE           | TXCIE             | UDRIE              | RXEN     | TXEN   |        | RXB8     | TXB8   |                   |

| \$0A (\$2A)          | UCSRB  |                 |                   |                    | HXEN     | IXEN   | UCSZ2  | HXB8     | 1XB8   | 163               |

| \$09 (\$29)          | UBRRL  |                 | Rate Register Li  |                    | 1000     |        |        |          |        | 165               |

| \$08 (\$28)          | ACSR   | ACD             | ACBG              | ACO                | ACI      | ACIE   | ACIC   | ACIS1    | ACIS0  | 200               |

| \$07 (\$27)          | ADMUX  | REFS1           | REFS0             | ADLAR              | MUX4     | MUX3   | MUX2   | MUX1     | MUX0   | 215               |

| \$06 (\$26)          | ADCSRA | ADEN            | ADSC              | ADATE              | ADIF     | ADIE   | ADPS2  | ADPS1    | ADPS0  | 217               |

| \$05 (\$25)          | ADCH   | ADC Data Rep    | gister High Byte  |                    |          | -      |        |          |        | 218               |

| \$04 (\$24)          | ADCL   | ADC Data Res    | gister Low Byte   |                    |          |        |        |          |        | 218               |

| \$03 (\$23)          | TWDR   |                 | al Interface Data | Register           | 20       |        |        | 100      |        | 180               |

|                      | TWAR   | TWA6            | TWA5              | TWA4               | TWA3     | TWA2   | TWA1   | TWA0     | TWGCE  | 180               |

6 ATmega16(L)

# ATmega16(L)

| Address     | Name | Bit 7          | Bit 6                                       | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Page |

|-------------|------|----------------|---------------------------------------------|-------|-------|-------|-------|-------|-------|------|

| \$01 (\$21) | TWSR | TWS7           | TWS6                                        | TWS5  | TWS4  | TWS3  | -     | TWPS1 | TWPS0 | 179  |

| \$00 (\$20) | TWBR | Two-wire Seria | Two-wire Serial Interface Bit Rate Register |       |       |       |       |       |       |      |

- | Notes: 1. When the OCDEN Fuse is unprogrammed, the OSCCAL Register is always accessed on this address. Refer to the debugger specific documentation for details on how to use the OCDR Register.

2. Refer to the USART description for details on how to access UBRRH and UCSRC.

3. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

4. Some of the Status Flags are cleared by writing a logical one to them. Note that the CBI and SBI instructions will operate on all bits in the I/O Register, writing a one back into any flag read as set, thus clearing the flag. The CBI and SBI instructions work with registers \$00 to \$1F only.

7

# **Instruction Set Summary**

| Mnemonics      | Operands         | Description                              | Operation                                             | Flags      | #Clocks |

|----------------|------------------|------------------------------------------|-------------------------------------------------------|------------|---------|

| ARITHMETIC AND | LOGIC INSTRUCTIO | NS                                       |                                                       |            |         |

| ADD            | Rd, Rr           | Add two Registers                        | Rd ← Rd + Rr                                          | Z,C,N,V,H  | 1       |

| ADC            | Rd, Rr           | Add with Carry two Registers             | $Rd \leftarrow Rd + Rr + C$                           | Z.C.N.V.H  | 1       |

| ADIW           | Rdl,K            | Add Immediate to Word                    | Rdh:Rdl ← Rdh:Rdl + K                                 | Z,C,N,V,S  | 2       |

| SUB            | Rd, Rr           | Subtract two Registers                   | Rd ← Rd - Rr                                          | Z,C,N,V,H  | 1       |

| SUBI           | Rd, K            | Subtract Constant from Register          | Rd ← Rd - K                                           | Z,C,N,V,H  | 1       |

| SBC            | Rd, Rr           | Subtract with Carry two Registers        | Rd ← Rd - Rr - C                                      | Z,C,N,V,H  | 1       |

| SBCI           | Rd, K            | Subtract with Carry Constant from Reg.   | Rd ← Rd - K - C                                       | Z,C,N,V,H  | 1       |

| SBIW           | RdI,K            | Subtract Immediate from Word             | Rdh:Rdl ← Rdh:Rdl - K                                 | Z,C,N,V,S  | 2       |

| AND            | Rd, Rr           | Logical AND Registers                    | Rd ← Rd • Rr                                          | Z,N,V      | 1       |

| ANDI           | Rd, K            | Logical AND Register and Constant        | Rd ← Rd • K                                           | Z,N,V      | 1       |

| OR             | Rd, Rr           | Logical OR Registers                     | $Rd \leftarrow Rd \vee Rr$                            | Z,N,V      | 1       |

| ORI            | Rd, K            | Logical OR Register and Constant         | Rd ← Rd v K                                           | Z,N,V      | 1       |

| EOR            | Rd, Rr           | Exclusive OR Registers                   | Rd ← Rd ⊕ Rr                                          | Z,N,V      | 1       |

| COM            | Rd               | One's Complement                         | Rd ← \$FF – Rd                                        | Z,C,N,V    | 1       |

| NEG            | Rd               | Two's Complement                         | Rd ← \$00 – Rd                                        | Z,C,N,V,H  | 1       |

| SBR            | Rd,K             | Set Bit(s) in Register                   | $Rd \leftarrow Rd \vee K$                             | Z,N,V      | 1       |

| CBR            | Rd,K             | Clear Bit(s) in Register                 | Rd ← Rd • (\$FF - K)                                  | Z,N,V      | 1       |

| INC            | Rd               | Increment                                | Rd ← Rd + 1                                           | Z,N,V      | 1       |

| DEC            | Rd               | Decrement                                | Rd ← Rd – 1                                           | Z,N,V      | 1       |

| TST            | Rd               | Test for Zero or Minus                   | Rd ← Rd • Rd                                          | Z,N,V      | 1       |

| CLR            | Rd               | Clear Register                           | Rd ← Rd ⊕ Rd                                          | Z,N,V      | 1       |

| SER            | Rd               | Set Register                             | Rd ← \$FF                                             | None       | 1       |

| MUL            | Rd, Rr           | Multiply Unsigned                        | R1:R0 ← Rd x Rr                                       | Z,C        | 2       |

| MULS           | Rd, Rr           | Multiply Signed                          | R1:R0 ← Rd x Rr                                       | Z,C        | 2       |

| MULSU          | Rd, Rr           | Multiply Signed with Unsigned            | R1:R0 ← Rd x Rr                                       | Z,C        | 2       |

| FMUL           | Rd, Rr           | Fractional Multiply Unsigned             | R1:R0 ← (Rd x Rr) << 1                                | Z,C        | 2       |

| FMULS          | Rd, Rr           | Fractional Multiply Signed               | R1:R0 ← (Rd x Rr) << 1                                | Z,C        | 2       |

| FMULSU         | Rd, Rr           | Fractional Multiply Signed with Unsigned | R1:R0 ← (Rd x Rr) << 1                                | Z,C        | 2       |

| BRANCH INSTRUC | CTIONS           |                                          |                                                       |            | 12      |

| RJMP           | k                | Relative Jump                            | PC ← PC + k + 1                                       | None       | 2       |

| IJMP           |                  | Indirect Jump to (Z)                     | PC ← Z                                                | None       | 2       |

| JMP            | k                | Direct Jump                              | PC ← k                                                | None       | 3       |

| RCALL          | k                | Relative Subroutine Call                 | PC ← PC + k + 1                                       | None       | 3       |

| ICALL          |                  | Indirect Call to (Z)                     | PC ← Z                                                | None       | 3       |

| CALL           | k                | Direct Subroutine Call                   | PC ← k                                                | None       | 4       |

| RET            |                  | Subroutine Return                        | PC ← STACK                                            | None       | 4       |

| RETI           |                  | Interrupt Return                         | PC ← STACK                                            | - 0        | 4       |

| CPSE           | Rd,Rr            | Compare, Skip if Equal                   | if $(Rd = Rr) PC \leftarrow PC + 2 \text{ or } 3$     | None       | 1/2/3   |

| CP             | Rd,Rr            | Compare                                  | Rd – Rr                                               | Z, N,V,C,H | 1       |

| CPC            | Rd,Rr            | Compare with Carry                       | Rd – Rr – C                                           | Z, N,V,C,H | 1       |

| CPI            | Rd,K             | Compare Register with Immediate          | Rd – K                                                | Z, N,V,C,H | 1       |

| SBRC           | Rr, b            | Skip if Bit in Register Cleared          | if (Rr(b)=0) PC ← PC + 2 or 3                         | None       | 1/2/3   |

| SBRS           | Rr, b            | Skip if Bit in Register is Set           | if $(Rr(b)=1) PC \leftarrow PC + 2 \text{ or } 3$     | None       | 1/2/3   |

| SBIC           | P, b             | Skip if Bit in I/O Register Cleared      | if (P(b)=0) PC ← PC + 2 or 3                          | None       | 1/2/3   |

| SBIS           | P, b             | Skip if Bit in I/O Register is Set       | if (P(b)=1) PC ← PC + 2 or 3                          | None       | 1/2/3   |

| BRBS           | s, k             | Branch if Status Flag Set                | if (SREG(s) = 1) then PC←PC+k + 1                     | None       | 1/2     |

| BRBC           | s, k             | Branch if Status Flag Cleared            | if $(SREG(s) = 0)$ then $PC \leftarrow PC + k + 1$    | None       | 1/2     |

| BREQ           | k                | Branch if Equal                          | if $(Z = 1)$ then PC $\leftarrow$ PC + k + 1          | None       | 1/2     |

| BRNE           | k                | Branch if Not Equal                      | if $(Z = 0)$ then $PC \leftarrow PC + k + 1$          | None       | 1/2     |

| BRCS           | k                | Branch if Carry Set                      | if (C = 1) then PC $\leftarrow$ PC + k + 1            | None       | 1/2     |

| BRCC           | k                | Branch if Carry Cleared                  | if $(C = 0)$ then $PC \leftarrow PC + k + 1$          | None       | 1/2     |

| BRSH           | k                | Branch if Same or Higher                 | if $(C = 0)$ then $PC \leftarrow PC + k + 1$          | None       | 1/2     |

| BRLO           | k                | Branch if Lower                          | if $(C = 1)$ then $PC \leftarrow PC + k + 1$          | None       | 1/2     |

| BRMI           | k                | Branch if Minus                          | if (N = 1) then PC ← PC + k + 1                       | None       | 1/2     |

| BRPL           | k                | Branch if Plus                           | if $(N = 0)$ then $PC \leftarrow PC + k + 1$          | None       | 1/2     |

| BRGE           | k                | Branch if Greater or Equal, Signed       | if $(N \oplus V = 0)$ then $PC \leftarrow PC + k + 1$ | None       | 1/2     |

| BRLT           | k                | Branch if Less Than Zero, Signed         | if $(N \oplus V= 1)$ then $PC \leftarrow PC + k + 1$  | None       | 1/2     |

| BRHS           | k                | Branch if Half Carry Flag Set            | if (H = 1) then PC $\leftarrow$ PC + k + 1            | None       | 1/2     |

| BRHC           | k                | Branch if Half Carry Flag Cleared        | if $(H = 0)$ then $PC \leftarrow PC + k + 1$          | None       | 1/2     |

| BRTS           | k                | Branch if T Flag Set                     | if (T = 1) then PC ← PC + k + 1                       | None       | 1/2     |

| BRTC           | k                | Branch if T Flag Cleared                 | if $(T = 0)$ then PC $\leftarrow$ PC + k + 1          | None       | 1/2     |

| DDIVO          | k                | Branch if Overflow Flag is Set           | if $(V = 1)$ then $PC \leftarrow PC + k + 1$          | None       | 1/2     |

| BRVS           |                  | Branch if Overflow Flag is Cleared       | if (V = 0) then PC ← PC + k + 1                       | None       | 17.2    |

8 ATmega16(L)

# ATmega16(L)

| Mnemonics        | Operands        | Description                                                 | Operation                                                                 | Flags        | #Clocks |

|------------------|-----------------|-------------------------------------------------------------|---------------------------------------------------------------------------|--------------|---------|

| BRIE             | k               | Branch if Interrupt Enabled                                 | if ( I = 1) then PC ← PC + k + 1                                          | None         | 1/2     |

| BRID             | k               | Branch if Interrupt Disabled                                | if ( I = 0) then PC ← PC + k + 1                                          | None         | 1/2     |

| DATA TRANSFER    | INSTRUCTIONS    |                                                             |                                                                           |              |         |

| MOV              | Rd, Rr          | Move Between Registers                                      | Rd ← Rr                                                                   | None         | 1       |

| MOVW             | Rd, Rr          | Copy Register Word                                          | Rd+1:Rd ← Rr+1:Rr                                                         | None         | 1       |

| LDI              | Rd, K           | Load Immediate                                              | Rd ← K                                                                    | None         | 1       |

| LD               | Rd, X           | Load Indirect                                               | $Rd \leftarrow (X)$                                                       | None         | 2       |

| LD               | Rd, X+          | Load Indirect and Post-Inc.                                 | $Rd \leftarrow (X), X \leftarrow X + 1$                                   | None         | 2       |

| LD               | Rd, - X         | Load Indirect and Pre-Dec.                                  | $X \leftarrow X - 1$ , $Rd \leftarrow (X)$                                | None         | 2       |

| LD               | Rd, Y           | Load Indirect                                               | $Rd \leftarrow (Y)$                                                       | None         | 2       |

| LD               | Rd, Y+          | Load Indirect and Post-Inc.                                 | Rd ← (Y), Y ← Y + 1                                                       | None         | 2       |

| LDD              | Rd, - Y         | Load Indirect and Pre-Dec.                                  | $Y \leftarrow Y - 1$ , $Rd \leftarrow (Y)$                                | None         | 2       |

| - Comment        | Rd,Y+q          | Load Indirect with Displacement  Load Indirect              | Rd ← (Y + q)                                                              | None<br>None | 2       |

| LD               | Rd, Z<br>Rd, Z+ | Load Indirect Load Indirect and Post-Inc.                   | $Rd \leftarrow (Z)$<br>$Rd \leftarrow (Z), Z \leftarrow Z+1$              | None         | 2 2     |

| LD               | Rd, -Z          |                                                             | $Z \leftarrow Z \cdot 1$ , $Rd \leftarrow (Z)$                            |              | 2       |

| LDD              | Rd, Z+q         | Load Indirect and Pre-Dec.  Load Indirect with Displacement | $Z \leftarrow Z \cdot 1$ , $Rd \leftarrow (Z)$<br>$Rd \leftarrow (Z + q)$ | None<br>None | 2       |

| LDS              | Rd, k           | Load Direct from SRAM                                       | Rd ← (k)                                                                  | None         | 2       |

| ST               | X, Rr           | Store Indirect                                              | $(X) \leftarrow Rr$                                                       | None         | 2       |

| ST               | X+, Br          | Store Indirect Store Indirect and Post-Inc.                 | (X) ← Rr, X ← X + 1                                                       | None         | 2       |

| ST               | - X, Rr         | Store Indirect and Pre-Dec.                                 | X ← X - 1, (X) ← Rr                                                       | None         | 2       |

| ST               | Y, Rr           | Store Indirect and Pre-Dec.                                 | (Y) ← Rr                                                                  | None         | 2       |

| ST               | Y+, Br          | Store Indirect and Post-Inc.                                | (Y) ← Rr, Y ← Y + 1                                                       | None         | 2       |

| ST               | - Y, Rr         | Store Indirect and Pre-Dec.                                 | Y ← Y - 1, (Y) ← Rr                                                       | None         | 2       |

| STD              | Y+q,Rr          | Store Indirect with Displacement                            | (Y + q) ← Rr                                                              | None         | 2       |

| ST               | Z, Rr           | Store Indirect                                              | (Z) ← Rr                                                                  | None         | 2       |

| ST               | Z+, Rr          | Store Indirect and Post-Inc.                                | (Z) ← Rr, Z ← Z + 1                                                       | None         | 2       |

| ST               | -Z, Rr          | Store Indirect and Pre-Dec.                                 | Z ← Z - 1, (Z) ← Br                                                       | None         | 2       |

| STD              | Z+q,Rr          | Store Indirect with Displacement                            | (Z + q) ← Rr                                                              | None         | 2       |

| STS              | k, Rr           | Store Direct to SRAM                                        | (k) ← Rr                                                                  | None         | 2       |

| LPM              | 14.10           | Load Program Memory                                         | R0 ← (Z)                                                                  | None         | 3       |

| LPM              | Rd, Z           | Load Program Memory                                         | Rd ← (Z)                                                                  | None         | 3       |

| LPM              | Rd, Z+          | Load Program Memory and Post-Inc                            | Rd ← (Z), Z ← Z+1                                                         | None         | 3       |

| SPM              | 1.00, 20.       | Store Program Memory                                        | (Z) ← R1:R0                                                               | None         | 1 .     |

| IN               | Rd, P           | In Port                                                     | Rd ← P                                                                    | None         | 1       |

| OUT              | P. Rr           | Out Port                                                    | P ← Rr                                                                    | None         | 1       |

| PUSH             | Rr              | Push Register on Stack                                      | STACK ← Rr                                                                | None         | 2       |

| POP              | Rd              | Pop Register from Stack                                     | Rd ← STACK                                                                | None         | 2       |

| BIT AND BIT-TEST | INSTRUCTIONS    |                                                             |                                                                           |              |         |

| SBI              | P,b             | Set Bit in I/O Register                                     | I/O(P,b) ← 1                                                              | None         | 2       |

| CBI              | P,b             | Clear Bit in I/O Register                                   | I/O(P,b) ← 0                                                              | None         | 2       |

| LSL              | Rd              | Logical Shift Left                                          | $Rd(n+1) \leftarrow Rd(n), Rd(0) \leftarrow 0$                            | Z,C,N,V      | 1       |

| LSR              | Rd              | Logical Shift Right                                         | $Rd(n) \leftarrow Rd(n+1), Rd(7) \leftarrow 0$                            | Z,C,N,V      | 1       |

| ROL              | Rd              | Rotate Left Through Carry                                   | $Rd(0)\leftarrow C,Rd(n+1)\leftarrow Rd(n),C\leftarrow Rd(7)$             | Z,C,N,V      | 1       |

| ROR              | Rd              | Rotate Right Through Carry                                  | $Rd(7)\leftarrow C_*Rd(n)\leftarrow Rd(n+1)_*C\leftarrow Rd(0)$           | Z,C,N,V      | 1       |

| ASR              | Rd              | Arithmetic Shift Right                                      | Rd(n) ← Rd(n+1), n=06                                                     | Z,C,N,V      | 1       |

| SWAP             | Rd              | Swap Nibbles                                                | Rd(30)←Rd(74),Rd(74)←Rd(30)                                               | None         | 1       |

| BSET             | s               | Flag Set                                                    | SREG(s) ← 1                                                               | SREG(s)      | 1       |

| BCLR             | s               | Flag Clear                                                  | $SREG(s) \leftarrow 0$                                                    | SREG(s)      | 1       |

| BST              | Rr, b           | Bit Store from Register to T                                | $T \leftarrow Rr(b)$                                                      | Т            | 1       |

| BLD              | Rd, b           | Bit load from T to Register                                 | Rd(b) ← T                                                                 | None         | 1       |

| SEC              |                 | Set Carry                                                   | C ← 1                                                                     | С            | 1       |

| CLC              |                 | Clear Carry                                                 | C ← 0                                                                     | С            | . 1     |

| SEN              |                 | Set Negative Flag                                           | N ← 1                                                                     | N            | 1       |

| CLN              |                 | Clear Negative Flag                                         | N ← 0                                                                     | N            | 1       |

| SEZ              |                 | Set Zero Flag                                               | Z ← 1                                                                     | Z            | 1       |

| CLZ              |                 | Clear Zero Flag                                             | Z ← 0                                                                     | Z            | 1       |

| SEI              |                 | Global Interrupt Enable                                     | I ← 1                                                                     | T.           | 1       |

| CLI              |                 | Global Interrupt Disable                                    | 1←0                                                                       | - E          | 1       |

| SES              |                 | Set Signed Test Flag                                        | S ← 1                                                                     | S            | 1       |

| CLS              |                 | Clear Signed Test Flag                                      | S ← 0                                                                     | S            | 1       |

| SEV              |                 | Set Twos Complement Overflow.                               | V ← 1                                                                     | V            | 1       |

| CLV              |                 | Clear Twos Complement Overflow                              | V ← 0                                                                     | V            | 1       |

| SET              |                 | Set T in SREG                                               | T ← 1                                                                     | Т            | 1       |

| CLT              |                 | Clear T in SREG                                             | T ← 0                                                                     | T            | 1       |

| SEH              |                 | Set Half Carry Flag in SREG                                 | H ← 1                                                                     | H            | 1 4     |

9

| Mnemonics   | Operands     | Description                   | Operation                                | Flags | #Clocks |

|-------------|--------------|-------------------------------|------------------------------------------|-------|---------|

| CLH         |              | Clear Half Carry Flag in SREG | H ← 0                                    | Н     | 1       |

| MCU CONTROL | INSTRUCTIONS |                               |                                          |       |         |

| NOP         |              | No Operation                  |                                          | None  | 1       |

| SLEEP       |              | Sleep                         | (see specific descr. for Sleep function) | None  | 1       |

| WDR         |              | Watchdog Reset                | (see specific descr. for WDR/timer)      | None  | 1       |

| BREAK       |              | Break                         | For On-Chip Debug Only                   | None  | N/A     |

10 ATmega16(L)

# **Ordering Information**

| Speed (MHz) | Power Supply | Ordering Code                                   | Package             | Operation Range               |  |

|-------------|--------------|-------------------------------------------------|---------------------|-------------------------------|--|

| 8           | 2.7 - 5.5V   | ATmega16L-8AC<br>ATmega16L-8PC<br>ATmega16L-8MC | 44A<br>40P6<br>44M1 | Commercial<br>(0°C to 70°C)   |  |

|             |              | ATmega16L-8AI<br>ATmega16L-8PI<br>ATmega16L-8MI | 44A<br>40P6<br>44M1 | Industrial<br>(-40°C to 85°C) |  |

| 16          | 4.5 - 5.5V   | ATmega16-16AC<br>ATmega16-16PC<br>ATmega16-16MC | 44A<br>40P6<br>44M1 | Commercial<br>(0°C to 70°C)   |  |

|             |              | ATmega16-16AI<br>ATmega16-16PI<br>ATmega16-16MI | 44A<br>40P6<br>44M1 | Industrial<br>(-40°C to 85°C) |  |

|      | Package Type                                                                    |  |  |  |  |  |  |  |

|------|---------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 44A  | 44-lead, Thin (1.0 mm) Plastic Gull Wing Quad Flat Package (TQFP)               |  |  |  |  |  |  |  |

| 40P6 | 40-pin, 0.600" Wide, Plastic Dual Inline Package (PDIP)                         |  |  |  |  |  |  |  |

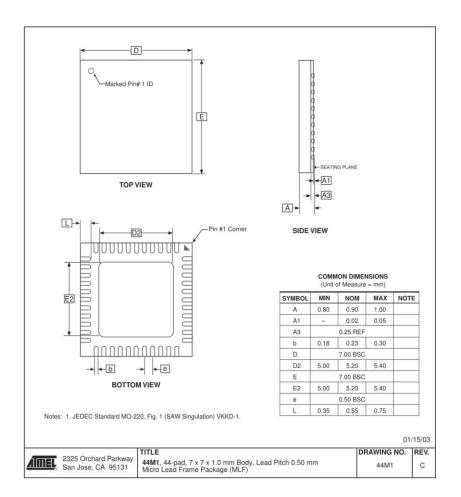

| 44M1 | 44-pad, 7 x 7 x 1.0 mm body, lead pitch 0.50 mm, Micro Lead Frame Package (MLF) |  |  |  |  |  |  |  |

11

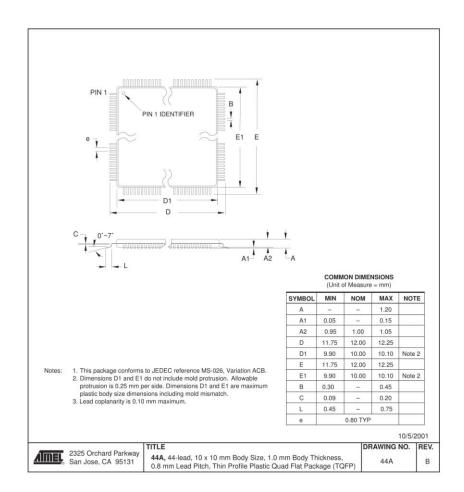

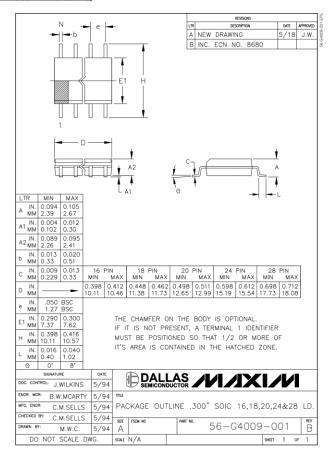

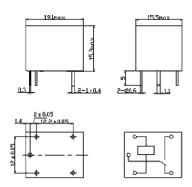

# **Packaging Information**

## 44A

12 ATmega16(L) =

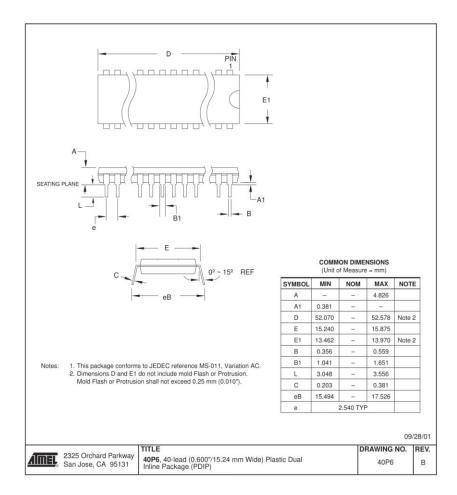

#### 40P6

2466HS-AVR-12/03

— <u>AIMEL</u>

13

#### 44M1

14 ATmega16(L) =

#### **Errata**

The revision letter in this section refers to the revision of the ATmega16 device.

#### ATmega16(L) Rev. I

#### · IDCODE masks data from TDI input

#### 1. IDCODE masks data from TDI input

The JTAG instruction IDCODE is not working correctly. Data to succeeding devices are replaced by all-ones during Update-DR.

#### Problem Fix / Workaround

- If ATmega16 is the only device in the scan chain, the problem is not visible.

- Select the Device ID Register of the ATmega16 by issuing the IDCODE instruction or by entering the Test-Logic-Reset state of the TAP controller to read out the contents of its Device ID Register and possibly data from succeeding devices of the scan chain. Issue the BYPASS instruction to the ATmega16 while reading the Device ID Registers of preceding devices of the boundary scan chain.

- If the Device IDs of all devices in the boundary scan chain must be captured simultaneously, the ATmega16 must be the fist device in the chain.

#### ATmega16(L) Rev. H

#### · IDCODE masks data from TDI input

#### 1. IDCODE masks data from TDI input

The JTAG instruction IDCODE is not working correctly. Data to succeeding devices are replaced by all-ones during Update-DR.

#### Problem Fix / Workaround

- If ATmega16 is the only device in the scan chain, the problem is not visible.

- Select the Device ID Register of the ATmega16 by issuing the IDCODE instruction or by entering the Test-Logic-Reset state of the TAP controller to read out the contents of its Device ID Register and possibly data from succeeding devices of the scan chain. Issue the BYPASS instruction to the ATmega16 while reading the Device ID Registers of preceding devices of the boundary scan chain.

- If the Device IDs of all devices in the boundary scan chain must be captured simultaneously, the ATmega16 must be the fist device in the chain.

#### ATmega16(L) Rev. G

#### IDCODE masks data from TDI input

#### 1. IDCODE masks data from TDI input

The JTAG instruction IDCODE is not working correctly. Data to succeeding devices are replaced by all-ones during Update-DR.

#### Problem Fix / Workaround

- If ATmega16 is the only device in the scan chain, the problem is not visible.

- Select the Device ID Register of the ATmega16 by issuing the IDCODE instruction or by entering the Test-Logic-Reset state of the TAP controller to read out the contents of its Device ID Register and possibly data from succeeding devices of the scan chain. Issue the BYPASS instruction to the ATmega16 while reading the Device ID Registers of preceding devices of the boundary scan chain.

15

If the Device IDs of all devices in the boundary scan chain must be captured simultaneously, the ATmega16 must be the fist device in the chain.

16 ATmega16(L) =

# Datasheet Change Log for ATmega16

This section contains a log on the changes made to the datasheet for ATmega16.

Changes from Rev. 2466G-10/03 to Rev. 2466H-12/03

All page numbers refer to this document.

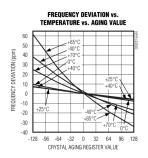

1. Updated "Calibrated Internal RC Oscillator" on page 27.

Changes from Rev. 2466F-02/03 to Rev. 2466G-10/03

All page numbers refer to this document.

- 1. Removed "Preliminary" from the datasheet.

- 2. Changed ICP to ICP1 in the datasheet.

- 3. Updated "JTAG Interface and On-chip Debug System" on page 34.

- 4. Updated assembly and C code examples in "Watchdog Timer Control Register WDTCR" on page 41.

- 5. Updated Figure 46 on page 101.

- Updated Table 15 on page 36, Table 82 on page 215 and Table 115 on page 274.

- 7. Updated "Test Access Port TAP" on page 220 regarding JTAGEN.

- 8. Updated description for the JTD bit on page 229.

- 9. Added note 2 to Figure 126 on page 251.

- 10. Added a note regarding JTAGEN fuse to Table 105 on page 259.

- 11. Updated Absolute Maximum Ratings\* and DC Characteristics in "Electrical Characteristics" on page 289.

- 12. Updated "ATmega16 Typical Characteristics" on page 297.

- 13. Fixed typo for 16 MHz MLF package in "Ordering Information" on page 11.

- 14. Added a proposal for solving problems regarding the JTAG instruction IDCODE in "Errata" on page 15.

Changes from Rev. 2466E-10/02 to Rev. 2466F-02/03

All page numbers refer to this document.

- Added note about masking out unused bits when reading the Program Counter in "Stack Pointer" on page 10.

- Added Chip Erase as a first step in "Programming the Flash" on page 286 and "Programming the EEPROM" on page 287.

- 3. Added the section "Unconnected pins" on page 53.

17

- 4. Added tips on how to disable the OCD system in "On-chip Debug System" on page 34.

- Removed reference to the "Multi-purpose Oscillator" application note and "32 kHz Crystal Oscillator" application note, which do not exist.

- 6. Added information about PWM symmetry for Timer0 and Timer2.

- Added note in "Filling the Temporary Buffer (Page Loading)" on page 252 about writing to the EEPROM during an SPM Page Load.

- 8. Removed ADHSM completely.

- Added Table 73, "TWI Bit Rate Prescaler," on page 180 to describe the TWPS bits in the "TWI Status Register – TWSR" on page 179.

- 10. Added section "Default Clock Source" on page 23.

- Added note about frequency variation when using an external clock. Note added in "External Clock" on page 29. An extra row and a note added in Table 118 on page 291.

- 12. Various minor TWI corrections.

- 13. Added "Power Consumption" data in "Features" on page 1.

- 14. Added section "EEPROM Write During Power-down Sleep Mode" on page 20.

- Added note about Differential Mode with Auto Triggering in "Prescaling and Conversion Timing" on page 205.

- 16. Added updated "Packaging Information" on page 12.

Changes from Rev. 2466D-09/02 to Rev. 2466E-10/02

All page numbers refer to this document.

1. Updated "DC Characteristics" on page 289.

Changes from Rev. 2466C-03/02 to Rev. 2466D-09/02

All page numbers refer to this document.

- 1. Changed all Flash write/erase cycles from 1,000 to 10,000.

- Updated the following tables: Table 4 on page 24, Table 15 on page 36, Table 42 on page 83, Table 45 on page 110, Table 46 on page 110, Table 59 on page 141, Table 67 on page 165, Table 90 on page 233, Table 102 on page 257, "DC Characteristics" on page 289, Table 119 on page 291, Table 121 on page 293, and Table 122 on page 295.

- 3. Updated "Errata" on page 15.

Changes from Rev. 2466B-09/01 to Rev. 2466C-03/02

All page numbers refer to this document.

1. Updated typical EEPROM programming time, Table 1 on page 18.

18 ATmega16(L) =

#### 2. Updated typical start-up time in the following tables:

Table 3 on page 23, Table 5 on page 25, Table 6 on page 26, Table 8 on page 27, Table 9 on page 27, and Table 10 on page 28.

- 3. Updated Table 17 on page 41 with typical WDT Time-out.

- 4. Added Some Preliminary Test Limits and Characterization Data.

Removed some of the TBD's in the following tables and pages:

Table 15 on page 36, Table 16 on page 40, Table 116 on page 272 (table removed in document review #D), "Electrical Characteristics" on page 289, Table 119 on page 291, Table 121 on page 293, and Table 122 on page 295.

5. Updated TWI Chapter.

Added the note at the end of the "Bit Rate Generator Unit" on page 176.

- Corrected description of ADSC bit in "ADC Control and Status Register A ADCSRA" on page 217.

- 7. Improved description on how to do a polarity check of the ADC doff results in "ADC Conversion Result" on page 214.

- 8. Added JTAG version number for rev. H in Table 87 on page 227.

- 9. Added not regarding OCDEN Fuse below Table 105 on page 259.

- 10. Updated Programming Figures:

Figure 127 on page 261 and Figure 136 on page 272 are updated to also reflect that AVCC must be connected during Programming mode. Figure 131 on page 268 added to illustrate how to program the fuses.

- 11. Added a note regarding usage of the "PROG\_PAGELOAD (\$6)" on page 278 and "PROG\_PAGEREAD (\$7)" on page 278.

- Removed alternative algorithm for leaving JTAG Programming mode.

See "Leaving Programming Mode" on page 286.

- Added Calibrated RC Oscillator characterization curves in section "ATmega16 Typical Characteristics" on page 297.

- 14. Corrected ordering code for MLF package (16MHz) in "Ordering Information" on page 11.

- 15. Corrected Table 90, "Scan Signals for the Oscillators<sup>(1)(2)(3)</sup>," on page 233.

19

#### **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### Regional Headquarters

Europe Atmel Sarl

Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland Tel: (41) 26-426-5555

Fax: (41) 26-426-5500

Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui

East Kowloon Hong Kong

Tel: (852) 2721-9778 Fax: (852) 2722-1369

Iapan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033

Japan

Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Atmel Operations**

Memory

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

Microcontrollers

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602

44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18 Fax: (33) 2-40-18-19-60

ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00 Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300

Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

RF/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0

Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300

Fax: 1(719) 540-1759

Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF Datacom

Avenue de Rochepleine BP 123

38521 Saint-Egreve Cedex, France

Tel: (33) 4-76-58-30-00 Fax: (33) 4-76-58-34-80

Literature Requests www.atmel.com/literature

Disclaimer: Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

© Atmel Corporation 2003. All rights reserved. Atmel® and combinations thereof, AVR®, and AVR Studio® are the registered trademarks of Atmel Corporation or its subsidiaries. Microsoft®, Windows®, Windows NT®, and Windows XP® are the registered trademarks of Microsoft Corporation. Other terms and product names may be the trademarks of others

# Lampiran 5. Datasheet IC 7805

February 1995

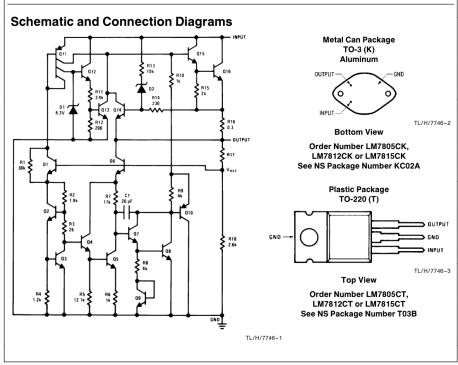

# **LM78XX Series Voltage Regulators**

## **General Description**

The LM78XX series of three terminal regulators is available with several fixed output voltages making them useful in a wide range of applications. One of these is local on card regulation, eliminating the distribution problems associated with single point regulation. The voltages available allow these regulators to be used in logic systems, instrumentation, HiFi, and other solid state electronic equipment. Although designed primarily as fixed voltage regulators these devices can be used with external components to obtain adjustable voltages and currents.

The LM78XX series is available in an aluminum TO-3 package which will allow over 1.0A load current if adequate heat sinking is provided. Current limiting is included to limit the peak output current to a safe value. Safe area protection for the output transistor is provided to limit internal power dissipation. If internal power dissipation becomes too high for the heat sinking provided, the thermal shutdown circuit takes over preventing the IC from overheating.

Considerable effort was expanded to make the LM78XX series of regulators easy to use and mininize the number

of external components. It is not necessary to bypass the output, although this does improve transient response. Input bypassing is needed only if the regulator is located far from the filter capacitor of the power supply.

For output voltage other than 5V, 12V and 15V the LM117 series provides an output voltage range from 1.2V to 57V.

#### **Features**

- Output current in excess of 1A

- Internal thermal overload protection

- No external components required

- Output transistor safe area protection

- Internal short circuit current limit

- Available in the aluminum TO-3 package

### **Voltage Range**

LM7805C 5V LM7812C 12V LM7815C 15V

© 1995 National Semiconductor Corporation TL/H/7746

RRD-B30M115/Printed in U. S. A.

# **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Input Voltage ( $V_O = 5V$ , 12V and 15V)

Internal Power Dissipation (Note 1)

Internal Voltage ( $V_O = 5V$ , 12V and 15V)

Internal Power Dissipation (Note 1) Internally Limited Operating Temperature Range ( $T_A$ ) 0°C to +70°C

Maximum Junction Temperature

(K Package)

150°C

(T Package)

150°C

Storage Temperature Range

-65°C to +150°C

Lead Temperature (Soldering, 10 sec.)

TO-3 Package K

TO-220 Package T

230°C

# $\textbf{Electrical Characteristics LM78XXC} \ \ (\text{Note 2}) \ \ 0^{\circ}\text{C} \le \text{Tj} \le 125^{\circ}\text{C unless otherwise noted}.$

35V

|                                        | Output Voltage                                                                                                         |                                                                                                                                                        |                                                                                                 |          |                               | 5V            |               | 12V                            |               |                | 15V                            |                |                            |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------|-------------------------------|---------------|---------------|--------------------------------|---------------|----------------|--------------------------------|----------------|----------------------------|

|                                        | Input Voltage (ເ                                                                                                       | ınless otherw                                                                                                                                          | rise noted)                                                                                     |          | 10V                           |               |               | 19V                            |               |                | 23V                            |                | Units                      |

| Symbol                                 | Parameter                                                                                                              |                                                                                                                                                        | Conditions                                                                                      | Min      | Тур                           | Max           | Min           | Тур                            | Max           | Min            | Тур                            | Max            |                            |

| Vo                                     | Output Voltage                                                                                                         | Tj = 25°C, 5                                                                                                                                           | $mA \le I_O \le 1A$                                                                             | 4.8      | 5                             | 5.2           | 11.5          | 12                             | 12.5          | 14.4           | 15                             | 15.6           | V                          |

|                                        |                                                                                                                        | $P_D \le 15W$ , 5 mA $\le I_O \le 1A$<br>$V_{MIN} \le V_{IN} \le V_{MAX}$                                                                              |                                                                                                 |          | ≤ V <sub>IN</sub>             | 5.25<br>≤ 20) | 11.4<br>(14.5 | ≤ V <sub>IN</sub>              | 12.6<br>≤ 27) | 14.25<br>(17.5 | $\leq V_{IN}$                  | 15.75<br>≤ 30) | V<br>V                     |

| ΔVO                                    | Line Regulation                                                                                                        | $\begin{array}{c} \Delta V_{IN} \\ \\ 0^{\circ}C \leq Tj \leq +125^{\circ}C \\ \\ \Delta V_{IN} \\ \\ I_{O} \leq 1A \\ \end{array}$ $Tj = 25^{\circ}C$ |                                                                                                 | (7 ≤     | 3<br>V <sub>IN</sub> ≤        | 50<br>(25)    | 14.5          | $\leq V_{IN}$                  | 120<br>≤ 30)  | (17.5          | $^{4} \leq v_{IN}$             | 150<br>≤ 30)   | mV<br>V                    |

|                                        |                                                                                                                        |                                                                                                                                                        |                                                                                                 | (8 ≤     | V <sub>IN</sub> ≤             | 50<br>(20)    | (15           | ≤ V <sub>IN</sub>              | 120<br>≤ 27)  | (18.5          | $\leq V_{IN}$                  | 150<br>≤ 30)   | mV<br>V                    |